PlanAhead allows the import of many different types of source files, including HDL and NGC cores. Open, edit, and develop RTL source files in the RTL editor. Below we introduce the [Sources] source file view and the use of the RTL editor.

1. Get to know the [Sources] source file view.Source file view display mode: Click in the [Sources] source file view window to maximize this window, as shown in Figure 10-9.

![[Sources] source file view - group by type](http://i.bosscdn.com/blog/0JP0OW_0.png)

Figure 10-9 [Sources] Source File View - Group by Type

The [Name] column in the figure shows the file name, which has three file types Core, Verilog, and VHDL. The [Library] column shows which library the corresponding source file belongs to. The [LocaTIon] column shows the file path. [Local] shows whether the import file is successful.

There are grouping modes in the upper right corner of the source file view window. There are 4 grouping methods, which are group by type, grouped by type, as shown in Figure 10-9, [Group by Source Root] is grouped by source file location. As shown in Figure 10-10, [Flat View] is leveled and grouped in alphabetical order, as shown in Figure 10-11.

![[Sources] source file view - group by location](http://i.bosscdn.com/blog/0J/I0/63/C_0.png)

Figure 10-10 [Sources] Source File View—Group by Location

![[Sources] source file view - grouped alphabetically](http://i.bosscdn.com/blog/0J/G1/15/57_0.png)

Figure 10-11 [Sources] Source File View - Grouped in alphabetical order

2. Specify the method of the library file.In the [Sources] source file view window shown in Figure 10-9, select the file other than bft.vhdl in the VHDL directory, right-click, select [Set Library...] in the pop-up menu, and enter the bftLib library in the [Set Library] window. name. As shown in Figure 10-12. Thus, a library file is specified for these VHDL files.

![[Set Library] window](http://i.bosscdn.com/blog/0J/FE/91/3_0.png)

Figure 10-12 [Set Library] window

3. RTL source file editor.Double-click the HDL file in the [Sources] window to open the RTL source file editor. In the editing window, the right-click pop-up menu allows the designer to perform various editing operations such as delete, copy, find, replace, and so on. If you click [Find in File], the dialog box shown in Figure 10-13 appears. Type clk and the software will find all the fields containing clk in the source file, as shown in Figure 10-14. Select a search result and double-click it. The corresponding source file will be opened and located in the source file.

Figure 10-13 Finding in the file

Figure 10-14 Finding results

Third, create an RTL source fileNew HDL source files can be created in PlanAhead, and language templates can also be used.

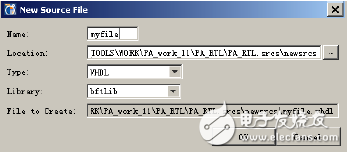

1. Right-click in the [Sources] window and select [Create Source...] in the pop-up menu to open the dialog shown in Figure 10-15. Enter the source file name, specifying the storage path, language type, and library name.

Figure 10-15 New Source File Dialog Box

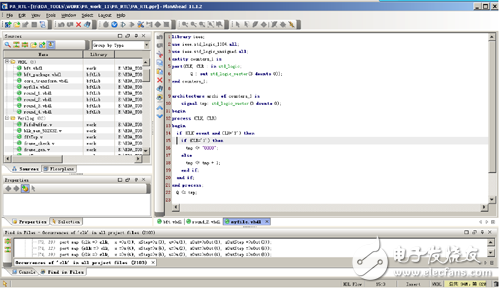

2. Click the [OK] button to open the myfile.vhdl window. Click the right-click menu in the empty space of this window and select [Insert Template...] to open the Xilinx language template, select a template, for example select a counter, click the [OK] button. This template will appear in the myfile.vhdl file, as shown in Figure 10-16. Of course, designers can enter their own HDL code here.

Figure 10-16 Creating a source program with a language template

Fourth, detection and analysis of RTL designPlanAhead provides RTL source detection, which can compile imported RTL source code. Compiled error and warning information can be displayed. This information can be used for cross-location, which is convenient for locating errors or warning sources. The RTL logic hierarchy can be expanded and can be used for various analyses. Once the probe function is used, all RTL views allow cross-probing of logical objects. The RTL netlist and hierarchical view show the logical hierarchy of the design. The RTL schematic view allows interactive logic probing. The find command can be used to find logical objects. The Instance Properties view displays information about the selected instance, including resource usage information. The RTL DRC tool tells the designer where power and performance optimizations are possible.

1. Run the RTL probe. In the menu bar, select [Tools] → [Run ElaboraTIon...], and the [Run ElaboraTIon] dialog box will pop up. As shown in Figure 10-17, enter top in the top module name and click the [OpTIons] field browse button to set the integration. Properties, click [Cancel] here, use the default value, click [OK] in the [Run Elaboration] dialog box to start RTL detection.

![[Run Elaboration] dialog box](http://i.bosscdn.com/blog/0J/61/13/104_0.png)

Figure 10-17 [Run Elaboration] dialog box

zhejiang ttn electric co.,ltd , https://www.ttnpower.com